CISC VS RISC

- CISC (Complex Instruction Set Computer)

- 하나의 instruction이 여러가지 복잡한 작업을 함 ex. move in x86

- instruction의 길이가 가변적

- ex. x86(Intel, AMD), Motorola 68k

- RISC (Reduced Instruction Set Computer)

- 각 instruction이 하나의 작은(unit) 작업만 함. ex. add, lw, sw, beq

- instruction의 길이가 고정됨

- Load/Store Architecture

- ex. RISC-V, ARM, MIPS

사실 이 그림이 왜 여기 그려져 있는지 했는데 일단 있으니까 설명을 해보도록 하죠

예를 들어 COPY라는 명령을 수행한다고 치자. hello라는 문자열을 복사하려고 한다.

hello는 현재 메모리에 100번지부터 104번지에 저장되어 있고, 우린 200번지부터 204번지까지로 복사하려 한다.

CPU에 source index는 100, destination index는 200, 그리고 옮겨야 할 개수가 5이므로 count 5로 시작한다.

100번지에 있는 h를 200 번지에 저장하고, count 1 감소, DI와 SI는 1 증가시킨다.

count가 0이 될 때까지 반복하면 끝!

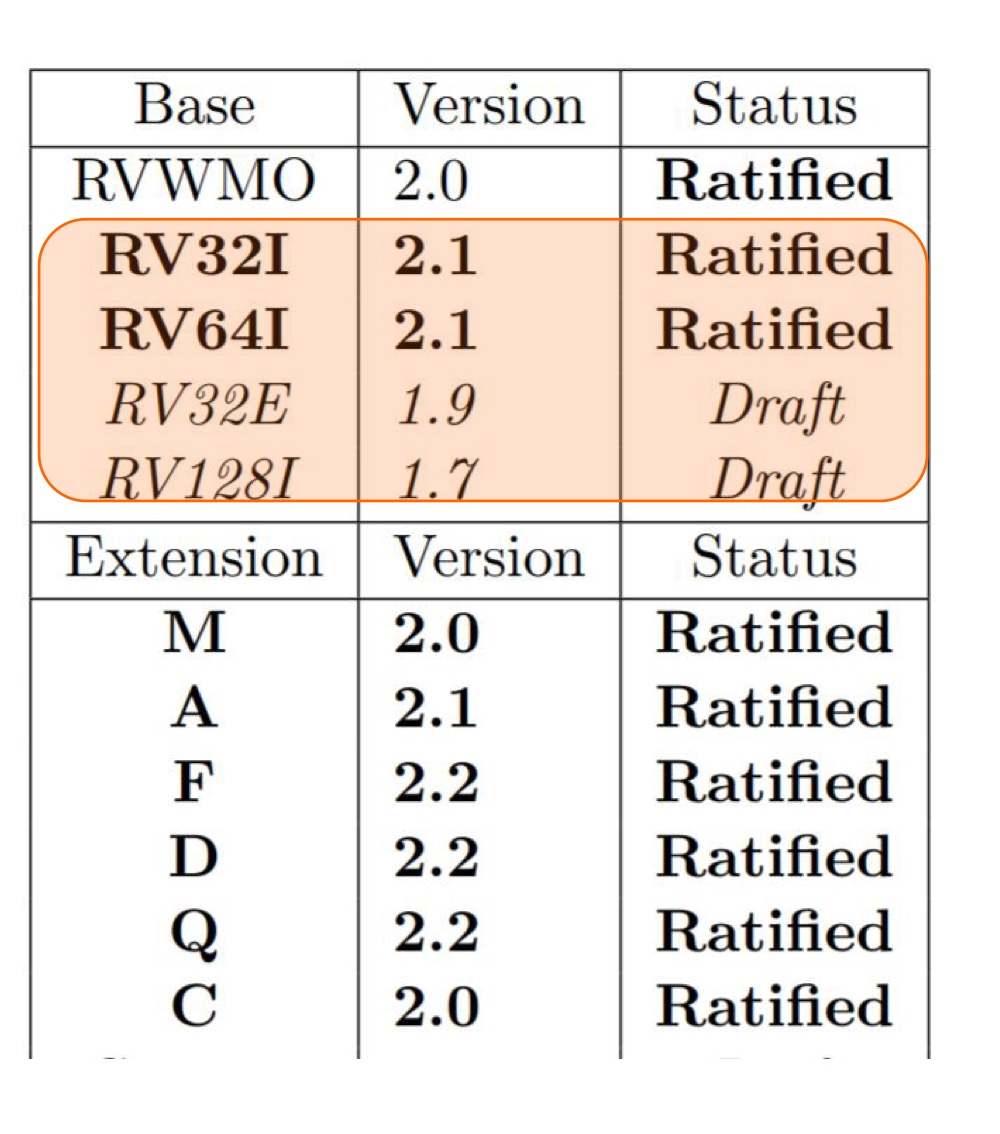

RISC-V ISA

: RISC-V는 ISAs와 관련된 제품군(?) 임

- RV32I : 32-bit architecture, base instruction set for Integer

- RV64I : 64-bit architecture, base instruction set for Integer

- RV32E : Subset of RV32I for small microcontrollers

- RV128I : 128-bit architecture

▪ M extension: Integer multiplication and division instructions

▪ A extension: Atomic instructions

▪ F extension: Single-precision floating-point instructions

▪ D extension: Double-precision floating-point instructions

▪ Q extension: Quad-precision floating-point instructions

▪ C extension: Compressed instructions

Instructions

CPU에 필요한 instructions 에 뭐가 있는지 알아보도록 합시다!

instruction에는 크게 세 가지 분류가 있음.

- Data processing instructions (Arithmetic and Logical)

- Memory access instructions (Load/Store)

- Branch instructions

이번 포스팅에서는 아마 1번만 다룰 것 같당

참고

CPU가 1GHz 라고 하면 10^9 Hz 이고, 1초에 10^9 번의 기본 연산(+, -, *, /) 을 할 수 있다는 것.

이러한 instruction 들이 존재한다.

A memory hierarchy

higher level 일 수록 속도는 더 빠르지만 비용이 훨씬 비싸고, lower level 일 수록 싼 대신 속도가 느리다

Overview of CPU Operation

add x5, x6, x7 # x5 = x6 + x7

이렇게 생긴 instruction이 있을 때, x6, x7 은 source operand가 되며, x5가 destination이 된다.

(# 이하는 주석임)

산술 명령의 피연산자(operand)는 레지스터라고 불리는 CPU 내부의 특정한 위치나, instructions의 immediate field 에서 불러온다.

(뒷 부분 알아야 이해감)

Register은 프로그래머가 볼 수 있음!!

(Cash는 볼 수 없음)

RISC-V에는 32개의 32bit register로 구성된 레지스터 파일이 있다 ㅇㅇ

RV32I Register File

1. 레지스터는 flip-flops으로 구성된다.

(32-bit register는 32개의 flip-flops이 필요함)

2. CPU 내부의 architectural register들의 집합을 register file이라고 부른다.

- 레지스터 파일은 flip-flops이나 SRAM으로 구성된다

- RV32I 레지스터 파일은 32개의 32-bit registers를 가지고 있다.

(두 개의 read ports와 한 개의 write port) - 레지스터 파일은 메인 메모리나 캐시에 접근하는 것보다 훨씬 빠름.

왜냐면 레지스터 수가 매우 제한되어 있고, CPU 내부에 있기 때문! - 그래서 컴파일러는 high-level code를 assembly code로 번역할 때 레지스터 파일을 사용하려고 함.

(레지스터 파일을 flip-flop 으로 구현해놓은 것이 피피티에 있으니 참고만 하자)

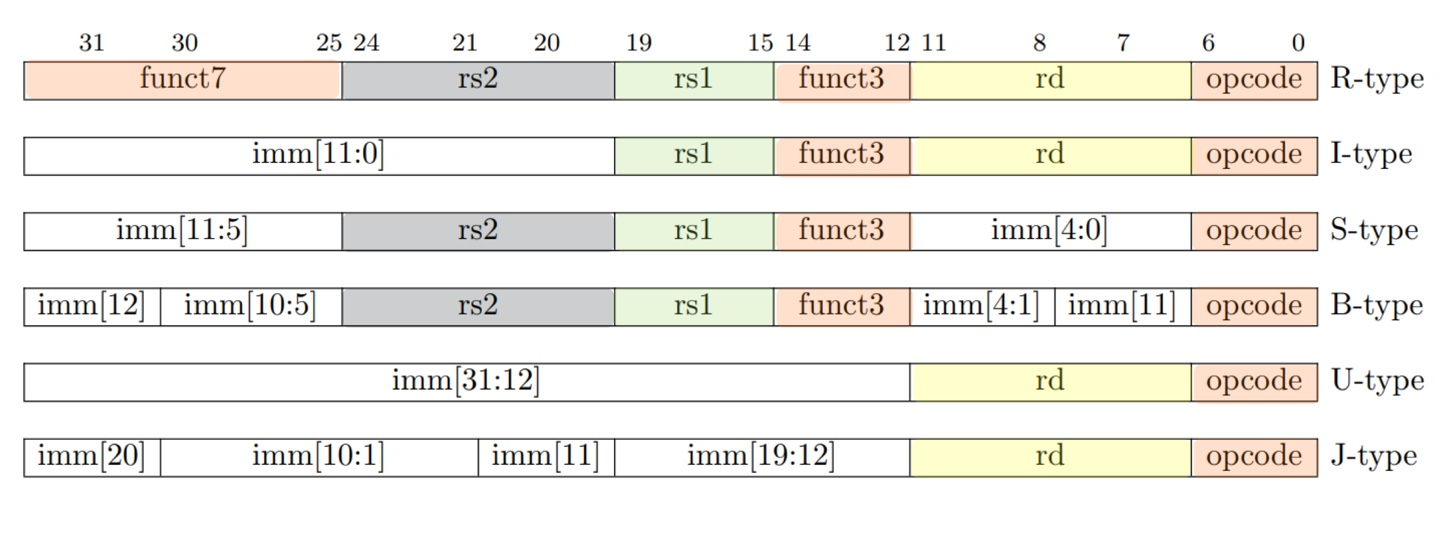

RISC-V Instruction Formats

Instruction Categories

- Arithmetic and Logical(Integer)

- Load/Store

- Jump and Branch

4개의 instruction formats 모두 32 bits 의 크기를 갖는다.

RISC-V Instruction Fields

32 bit로 구성되는 instruction에는 다음과 같은 field들이 있다.

- opcode, funct7, funct3 은 어떤 operation을 수행해야 하는지 명시한다. 이 셋을 합쳐서 총 2^17 = 128*1024 개의 각기 다른 operations을 수행할 수 있다.

- rs1 은 첫번째 source operand의 register 주소라고 보면 됨

- rs2 는 당연히 두 번째 source operand 의 register 주소

- rd는 destination operand의 register

* 참고 : encoding space를 무조건 전부 다 사용하는 것은 아님.

RV32I Arithmetic Instructions (add, sub, addi)

1. add

- R-Type instruction

add rd, rs1, rs2

ex.add t0, s1, s2 # t0 <= s1 + s2

rd = t0, rs1 = s1, rs2 = s2

- opcode : add 가 저장된 51번지

- rs1과 rs2는 s1, s2이므로 이들이 저장된 곳은 레지스터의 9번지와 18번지

- rd 역시 t0가 저장된 곳은 5번지

- 이 숫자를 binary로 표현하면

funct7 : 0000000 (7bit)

rs2 : 10010 (5bit)

rs1 : 01001 (5bit)

funct3 : 000 (3bit)

rd : 00101 (5bit)

opcode : 0110011 (7bit)

4개씩 끊어서 16진수로 바꿔주면 끝!

2. sub

- R-Type instruction

sub rd, rs1, rs2

ex.sub t2, s3, s4 # t2 <= s3 + s4

rd = t2, rs1 = s3, rs2 = s4'

Immediate 란 ?

- R-format instruction의 경우 레지스터에서 3개의 피연산자를 모두 가져오지만,

I-format instruction의 경우, 한 개의 피연산자를 instruction 자기 자신에게 저장할 수 있음 - 그 값을 immediates라고 부른다. 왜? 바로 instructions에서 바로! 접근 가능하기 때문!

register나 memory access를 필요로 하지 않는다. - 12 bit의 immediate field는 2의 보수를 활용할 경우 -2^11 ~ +2^11-1 의 범위까지 저장 가능하다.

- 컴퓨터 산술의 하드웨어 설계에서 2의 보수를 활용함으로써, unsigned number와 signed number의 덧셈 뺄셈을 편리하고 간단하게 할 수 있음!

2의 보수

n-bit number N 이 이진수로 주어졌을 때, N의 2의 보수는 다음과 같이 정의된다.

2^n - N for N != 0

0 for N = 0ex. 4 bit 일 때, 3은 4'b0011이고 이의 2의 보수는 3: 2^4-3 = 4'b1101

좀 더 쉽게 설명하자면

2진수에서 0,1을 뒤집어주고 1을 더해주면 된다.

'''''

4

= 0000 0100

-> 1111 1011

+1

= 1111 1100 = -4

N bit 로 나타낼 수 있는 범위는

- Unsigned : [ 0, 2^N-1 ]

- Sign/Magnitude : [ -(2^(N-1) -1), 2^(N-1) -1]

- 2의 보수 : [ -2^(N-1) , 2^(N-1) -1]

만약 12 bit라면

- Unsigned : 0~4095

- Sign/Magnitude : -2047 ~ +2047

- 2의 보수 : -2048 ~ +2047

의 범위를 나타낼 수 있다!

그리고 어떤 숫자가 +인지 -인지는 int로 선언했는지 unsigned로 선언했는지 봐서 프로그래머의 해석에 따라 달라진다.

3. addi

- I-Type instruction

addi rd, rs1, imm12

ex.addi t0, s3, -12 # t0 <= s3 + (-12)

rd = t0, rs1 = s3, imm12 = -12

- imm12 에 할당된 bit는 총 12 bit

- 따라서 다른 피연산자(32 bit)와 맞추려면 20bit를 무언가로 채워야 함. 이 때 나오는 개념이 extension

- zero-ext : 자료형의 확장 시 비었던 부분을 0으로 채운다

- sign-ext : 자료형의 확장 시 비었던 부분을 MSB(가장 왼쪽의 비트)로 채운다.

add, sub 처럼 arith inst 에는 SE 를 주로 사용하고,

andi 와 같은 logical inst 에는 ZE를 주로 사용한다.

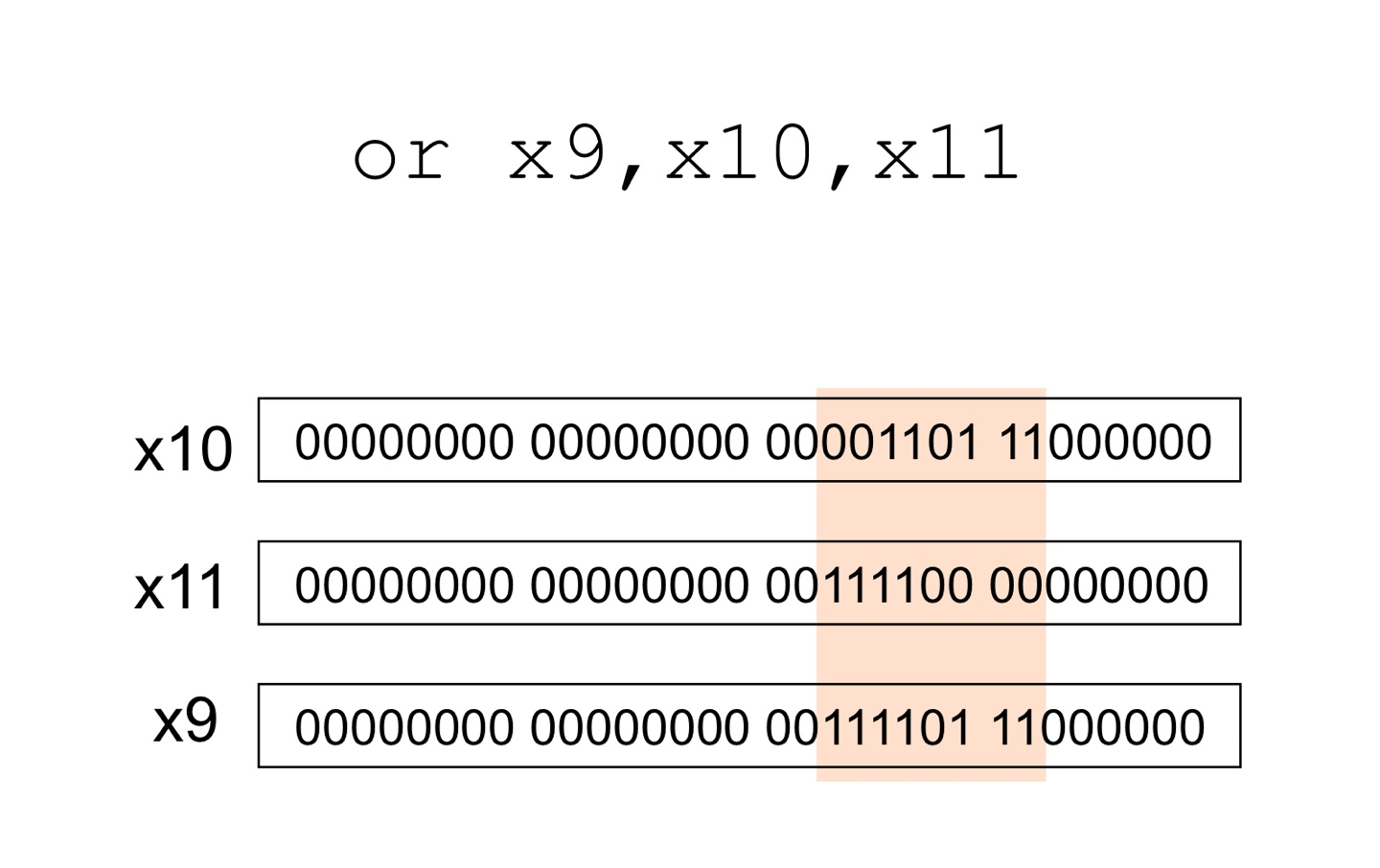

RV32I Logical Instructions (and, or, xor, andi, ori, xori)

-> logical instructions은 2개의 source operands에 대해 bit-by-bit 연산 수행 후 destination register에 값을 쓰는 것.

1. AND Instruction

-> bits masking 에 유용함(일부 비트만 살리고, 나머지 싹 0으로 초기화)

2. OR Instruction

-> bits combine에 유용함 (몇 비트를 1로 설정하고, 나머지는 그대로 둔다)

3. XOR Instruction

-> bits를 invert(reverse)하거나 0으로 초기화 할 때 유용함

첫 번째 경우 비트를 1111...과 xor하면 비트가 뒤집히고

아래의 경우 같은 비트를 xor하면 0으로 초기화된다.

위 세 가지 모두 R-Type Instruction

4. andi, ori, xori

- I-Type instruction

- immediates in these are sign-extended

- (뭐여 앞에선 ze 주로 쓴다매 뭐여)

Revisiting Basic Shifting

one left shift = 2배

one right shift = 1/2 배1. Revisiting Logical Shift

- Logical shift left

- MSB : shifted out

- LSB : shifted in with a 0

- ex) 1100 1011 << 1 = 100 1011 0

1100 1011 << 3 = 0 1011 000

- Logical shift right

- MSB : shifted in with a 0

- LSB : shifted out

- ex) 1100 1011 >> 1 = 0 110 0101

1100 1011 >> 3 = 000 1 1001

Logical shifts는 unsigned integer를 2의 제곱수로 나누거나, 2의 제곱수를 곱할 때 편리하다.

(( logical shift right는 나눠서 integer 가 아니면 버림한다))

2. Revisiting Arithmetic Shift

- Arithmetic shift left

- MSB : shifted out, 그러나 overflow/underflow를 조심할 것

- LSB : shifted in with a 0

- ex) 1100 <<< 1 = 100 0

1100 <<< 3 = 0 000 (incorrect!) => underflow

- Arithmetic shift right

- MSB : Retain its sign bit (밀린 부분에 가장 왼쪽 비트 이어서 확장해주기)

- LSB : Shifted out

- ex) 1100 >>> 1 = 1 110 (retain sign bit)

1100 >>> 3 = 111 1

((마찬가지로 나눠서 integer가 아니면 버린다))

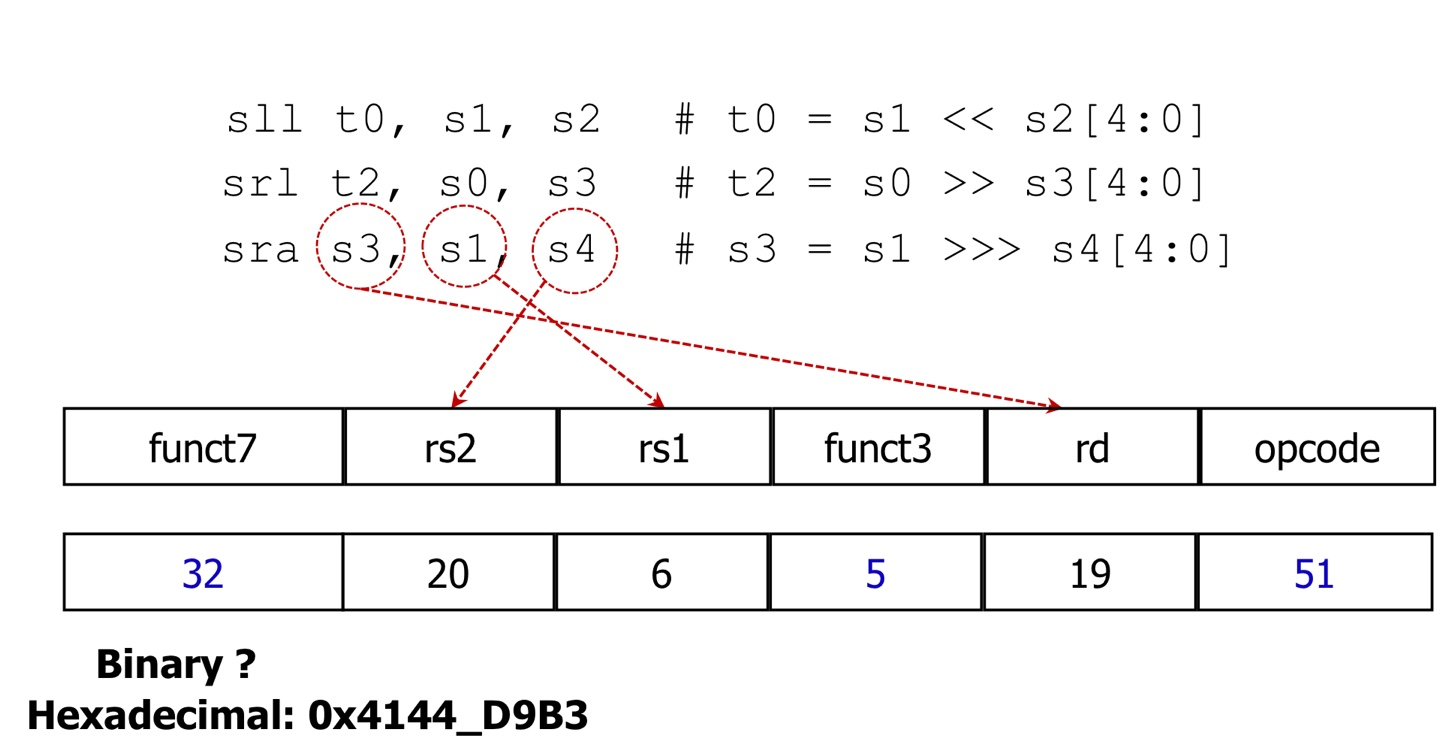

RV32I Shift Instructions (sll, srl, sra, slli, srli, srai)

-> Shift-left operation은 2의 제곱수로 곱하기

-> Shift-right operation은 2의 제곱수로 나누기

1. sll, srl, sra

- R type instructions

- sll rd, rs1, rs2[4:0] : shift left logical

- srl rd, rs1, rs2[4:0] : shift right logical

- sla rd, rs1, rs2[4:0] : shift right arithmetic (sign-extension)

다음과 같이 쓴다

2. slli, srli, srai

- Specialization of I type

- shift rs1 by up to 31 bits (5-bit shamt field)

- slli rd, rs1, shamt : shift left logical

- srli rd, rs1, shamt : shift right logical

- srai rd, rs1, shamt : shift right arithmetic (sign-extension)

'𝓡𝓸𝓸𝓶5: 𝒦𝑜𝓇𝑒𝒶 𝒰𝓃𝒾𝓋 > Computer Architecture(COSE222)' 카테고리의 다른 글

| [컴퓨터구조] CH4. RISC-V & RISC-V Instruction #3 (0) | 2021.10.16 |

|---|---|

| [컴퓨터구조] CH4. RISC-V & RISC-V Instruction #2 (0) | 2021.10.13 |

| [컴퓨터구조] CH3. Performance (0) | 2021.10.09 |

| [컴퓨터구조] CH2. Instructions and High-level to Machine Code (0) | 2021.10.08 |

| [컴퓨터구조] CH1. Computer and Technology (0) | 2021.10.08 |